Recent Advances in Die-Attach Film Adhesives

Die-attach film adhesives can enable more advanced technology for packaging semiconductor devices.

Using die-attach film at the wafer level compared to using die-attach material on individual die offers many benefits. To completely take advantage of the use of die-attach film at the wafer level, the die-attach film has to be optimized to account for various process conditions that the film has to successfully pass through without degradation in any of its end use properties, including adhesion strength and thermal and electrical properties.

Recently, the demand for handheld devices has led to more advanced technologies in 2.5-D and 3-D packaging, and in the handling of extremely thin wafers and dies. The material supply industry has responded by providing newer generations of die-attach films and wafer protection material to these increasingly demanding challenges. Packaging using wire-bonding, flip-chip soldering or the direct mechanical contact attach from flip-chip to bond pads effectively dictates the choice of different wafer level die-attach solutions.

Interconnections at the Wafer Level

In high-volume commercial applications, the use of 10-20 micron die-attach film adhesive has been proven to be reliable for stack-chip from 2-3 layers. The 10-20 micron film adhesive not only yields thinner devices that are attractive for tablets, cell phones, and cameras, but it also provides more uniform and controlled flow of the adhesive—and thus more reproducible interconnections.

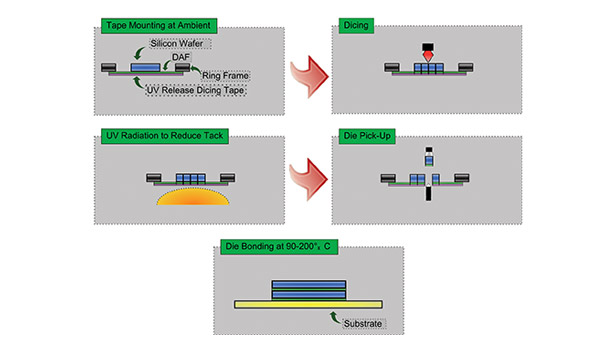

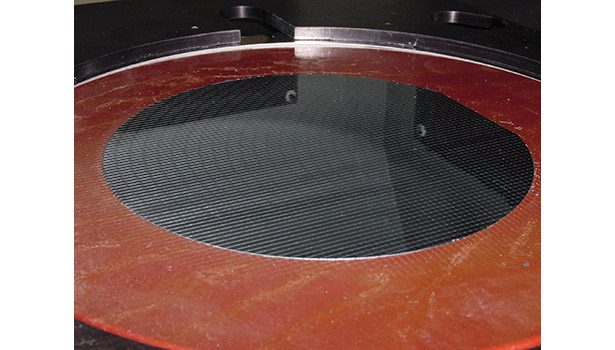

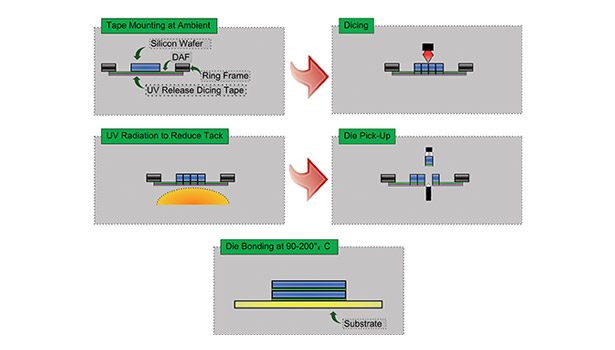

The standard wire-bonding chip packaging uses backside die attach that can use more traditional epoxy die-attached film adhesives that are available from die-attach film adhesive manufacturers from the U.S.1 and Japan. Typical manufacturing processes using wafer-level packaging are now integrated in terms of using dicing tape and die attach film that are directly laminated on the wafer before dicing. The material technology challenges that allow for these processes have been met so far by dicing die-attach film (DDAF) adhesives from the U.S. and Japan. These challenges include:

• Very thin and stable film adhesive (typically epoxy based) of 10-25 micron

• DAF film adhesive must be compatible with the adhesive layer of the dicing tape to prevent cross-contamination leading to residues and other side effects

• Ability to allow chip-stack bonding with high efficiency

• Ability to provide die-bonding stability for wire-bonding operation of up to 250°C for the highest production rate possible

• Most of the existing DDAF are meeting the performance requirements of at least JEDEC IPC level 3 or better for moisture sensitivity after packaging

• Depending on the bonding stability and moisture sensitive properties of DAF and the molding, encapsulation or other electro-mechanical protection, the finished devices range from level 3 in most cases and for the best solution meeting the level 1 requirement

• In case of high-temperature applications beyond the typical 125-150°C, newer non-epoxy DAF can now withstand long-term usage of 200°C and beyond

Advanced Die Bonding and Stress Relief

Traditional flip chip uses wire-bonding and solder-bump reflow for most requirements. The higher speed, performance and cost continue to drive semiconductor packaging toward a shorter path of interconnections between each level of the stack-chip packages.

The need to lower the cost of packaging has led to many innovative packaging solutions. The lowest cost electronic devices such as UHF RFID tags have been produced using direct flip-chip mechanical compression contact successfully in large volume.2 However, they are limited to an operating temperature of less than 60°C and they are not very stable against moisture. The fact that contact resistance can be properly maintained for long-term use within specified temperature and environmental constraints provides hope that solutions for high-performance applications can be achieved with more engineered materials and packaging.

The key for performance with this type of package is the flip-chip underfill that must also perform as a stable die-bonding adhesive. For flip- chip underfill adhesives to function properly, they must have the following characteristics:

• Must be easily placed either on the substrate or on the interconnection front side of the chip. DDAF will still be applicable. If the paste underfill adhesive is to be useful, it must stay in place after dispensing onto the substrate or chip.

• Must not prevent contact when the chip and package substrate interconnections are lined and compressed for bonding. Unlike the use of Z-axis, uni-axial, conductive adhesive, any particulate could be detrimental for the achievement of interconnections.

• Should have high glass-transition temperature and modulus to maintain the electrical contact and characteristics. For commercial and military applications, it should be well above 150°C.

• Should be as low in coefficient of thermal expansion (CTE) as that of higher filled traditional epoxy underfills (< 30 ppm/°C).

• Must be capable of curing at 175-250°C in less than 10 seconds in order to provide reasonable productivity.

• Must have moisture absorption be well below 0.5% in saturation to meet the JEDEC/IPC Level 1 moisture sensitivity requirements.

Non-epoxy-based, high-temperature, underfill adhesives in paste or film format are available in thickness of 25-75 micron for such applications.

Through Silicon Via Interconnection

Through silicon via (TSV)3 stack chip packaging represents the ultimate chip interconnection performance for stack chip packages. The requirement for stress relief is even more critical to filling in the vias of the TSV structure and between the stacking chips. For filling in the TSV vias, the specialty fill-in-adhesive requires at the following characteristics:

• Must have extreme low viscosity to wick into the vias easily with the capillary forces.

• Must have very low CTE once cured, preferably substantially below 30 ppm/°C.

• Must have high glass-transition temperature and modulus to maintain the electrical contact and characteristics. For commercial and military applications, it should be well above 150°C.

• Should cure in less than 10 seconds at 175-250°C.

There are now non-epoxy based high temperature fill-in paste adhesives that can easily fill-in the vias of 20 micron for such applications.

Overcoming Challenges

Wafer level die-attach films with very thin bond line have traditionally had many challenges. Recent advances in die-attach materials, along with optimized processing conditions, can overcome these challenges and will enable more advanced technology for packaging semiconductor devices within smaller footprint and volume. Similarly, flip-chip underfill adhesives can also enable effective fill in of through silicon vias while providing stress relief between stack chips.

For more information, visit www.aitechnology.com.

References

1. AI Technology Inc., www.aitechnology.com/products/dieattach.

2. “Alien Technology and RFID: Roll-to-roll Processing of Silicon-Based Microelectronics,” www.nist.gov.

3. “3D-TSVs Spark Packaging Revolution,” www.eetasia.com.

Looking for a reprint of this article?

From high-res PDFs to custom plaques, order your copy today!